Das Konzipieren von neuen Produkten auf 300 mm-Waferbasis, benötigt erhebliche Prozessentwicklungen und hohe Standards und damit auch hohe Kosten. In der Regel gibt es viele Kunden zum Beispiel in der Supplier-Branche, die jedoch für die eigene Weiterentwicklung ihrer Produkte fertige Vehikel brauchen oder zumindest ein „Proof-of-Concept“ um ihr eigenes Risiko zu minimieren. Erst dann kann oft entschieden werden ob die Testwafer deren Anspruch für Forschungs- und Entwicklungsaufgaben genügen und werden gegebenenfalls angepasst.

Durch die engmaschige Verknüpfung von Prozesstechnologieentwicklung, applikationsspezifischen Anwendungen und Analytik sowohl beim Fraunhofer IPMS-CNT als auch beim IZM-ASSID werden Synergien gewonnen, die es im Leistungszentrum ermöglichen anspruchsvolle strukturierte Testvehikel und Testsubstrate zu schaffen und anzubieten. Diese können sowohl direkt zur Evaluation Kunden und Partnern zur Verfügung gestellte werden, als auch in weiteren Industrieprojekten eingesetzt werden.

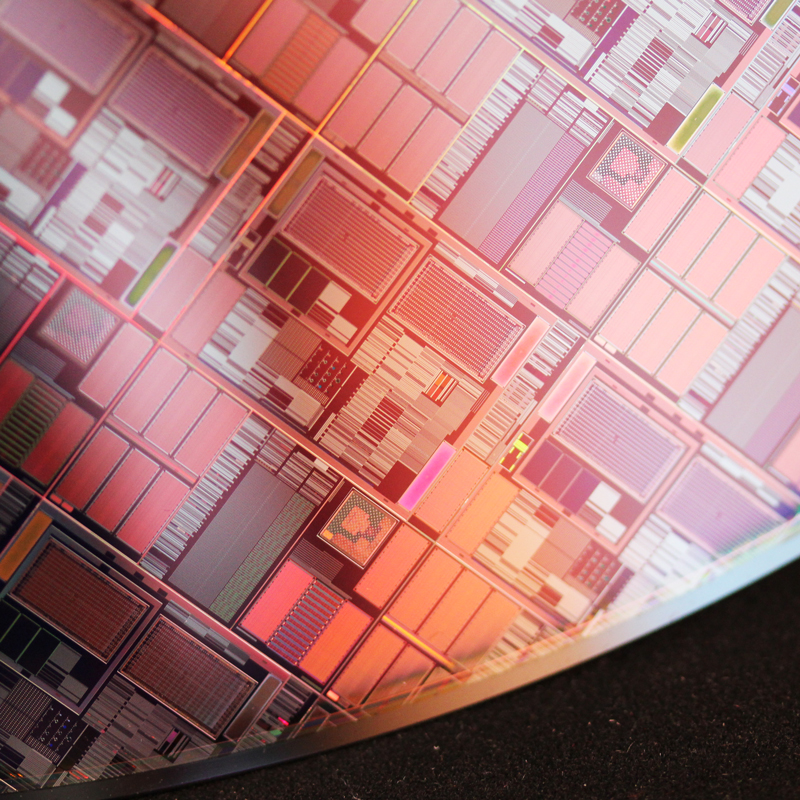

Das Projekt Testwafer Hub zielt auf die Schaffung einer professionalisierten Umgebung für das Anbieten von solchen 300 mm Testwafern. Die Technologien kommen dabei sowohl von Front-End-of-Line (FEoL), in dem High-k und epitaktische Si(Ge)-Schichten angeboten werden, als auch vom Back-End-of-Line (BEoL) und Packaging in denen die Metallisierung vor allem mittels Kupfer und dessen Einbettung eine Rolle spielt. Das Spannungsfeld hier geht dann von der reinen Entwicklung von Schichten bzw. Schichtstapel, über 3D-Auskleidung bis hin zur Strukturierung und elektrischer Charakterisierung. Neue und alte Anlagen in Kombination mit der Erfahrung in ganzen Prozessketten sollen dabei helfen das Produktportfolio durch anspruchsvolle und innovative Materialien, bzw. Testvehikel zu erweitern.

Leistungszentrum »Funktionsintegration für die Mikro-/Nanoelektronik«

Leistungszentrum »Funktionsintegration für die Mikro-/Nanoelektronik«